Οι Nehalem "δανείζονται" την αριτεκτονική των Barcelona

Εντάξει, δε δανείζονται εξ ολοκλήρου την αρχιτεκτονική που αφάρμοσε η AMD στους Barcelona - Phenom αλλά τη δομή που θα έχει η cache του επεξεργαστή.

Εντάξει, δε δανείζονται εξ ολοκλήρου την αρχιτεκτονική που αφάρμοσε η AMD στους Barcelona - Phenom αλλά τη δομή που θα έχει η cache του επεξεργαστή.

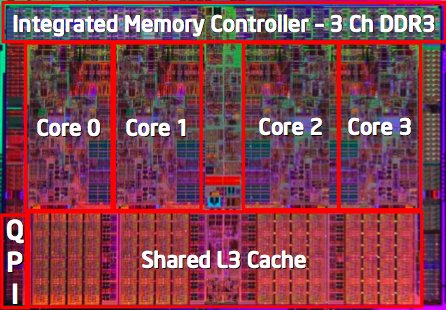

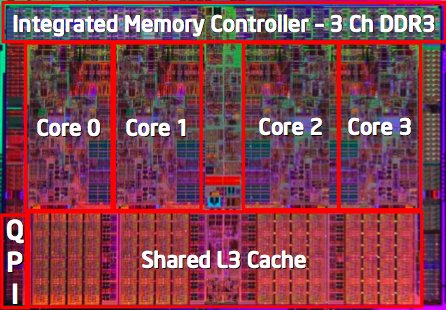

Αφήνοντας πίσω της το απαρχαιωμένο Front Side Bus (FSB) και χρησιμοποιώντας τον ενσωματωμένο ελεγκτή μνήμης καθώς και το QPI (Quick Path Interconnect) ήρθε και η στιγμή να αλλάξει και η δομή της CPU cache. Έτσι κάθε πυρήνας θα έχει τη δική του L1 cache (64KB), μία μικρότερη (σύμφωνα με τα σημερινά δεδομένα) L2 cache (256KB) καθώς και μία κοινή για όλους τους πυρήνες L3 cache (8MB).

[ Διαβάστε περισσότερα εδώ...]

|

Αφήνοντας πίσω της το απαρχαιωμένο Front Side Bus (FSB) και χρησιμοποιώντας τον ενσωματωμένο ελεγκτή μνήμης καθώς και το QPI (Quick Path Interconnect) ήρθε και η στιγμή να αλλάξει και η δομή της CPU cache. Έτσι κάθε πυρήνας θα έχει τη δική του L1 cache (64KB), μία μικρότερη (σύμφωνα με τα σημερινά δεδομένα) L2 cache (256KB) καθώς και μία κοινή για όλους τους πυρήνες L3 cache (8MB).

Disse:

It's a logical move for Intel as it was for AMD. The exclusive L2 caches give each core a pool of fast-access memory, while the shared cache acts as a buffer to trap data and instructions other cores may have requested and which another core can now grab more quickly that going out to main memory or peeking onto other cores' personal storage.

More to the point, since Nehalem is essentially Intel's first design - as AMD's have been for some time - that doesn't build four-core CPUs out of groups of two two-core dies. With no shared L3, the core-pairs in today's Core 2 Quad and Core 2 Extreme processors have to look in other core-pairs' caches, which can hinder performance.

It's a logical move for Intel as it was for AMD. The exclusive L2 caches give each core a pool of fast-access memory, while the shared cache acts as a buffer to trap data and instructions other cores may have requested and which another core can now grab more quickly that going out to main memory or peeking onto other cores' personal storage.

More to the point, since Nehalem is essentially Intel's first design - as AMD's have been for some time - that doesn't build four-core CPUs out of groups of two two-core dies. With no shared L3, the core-pairs in today's Core 2 Quad and Core 2 Extreme processors have to look in other core-pairs' caches, which can hinder performance.

[ Διαβάστε περισσότερα εδώ...]