AMD Zen 2: Η νέα Αρχιτεκτονική σε Βάθος

Τι περιλαμβάνουν στο εσωτερικό τους οι νέοι επεξεργαστές Ryzen της AMD; Τι αλλαγές έχουν γίνει από την πρώτη και τη δεύτερη γενιά;

Η είσοδος της Zen 2 αρχιτεκτονικής στην consumer αγορά σηματοδοτεί παράλληλα και ένα μεγάλο βήμα εξέλιξης για την AMD. Περίπου 25 μήνες μετά την κυκλοφορία των πρώτων επεξεργαστών η εταιρία έχει δρομολογήσει άπειρα updates στις δύο γενιές επεξεργαστών της όμως όπως μας είχε υποσχεθεί πριν καιρό, η Zen 2 θα ήταν ένα σημαντικό βήμα μπροστά - όπως η πρώτη γενιά Zen για τους Excavator, την τελευταία παραλλαγή της Bulldozer αρχιτεκτονικής. Έτσι λίγο πριν δούμε και επίσημα τους επεξεργαστές στα καταστήματα στις 7 Ιουλίου έχουμε για πρώτη φορά μια ολοκληρωμένη εικόνα της νέας αρχιτεκτονικής που ανέπτυξε η AMD, την οποία θα αναλύσουμε σε βάθος στο παρακάτω κείμενο.

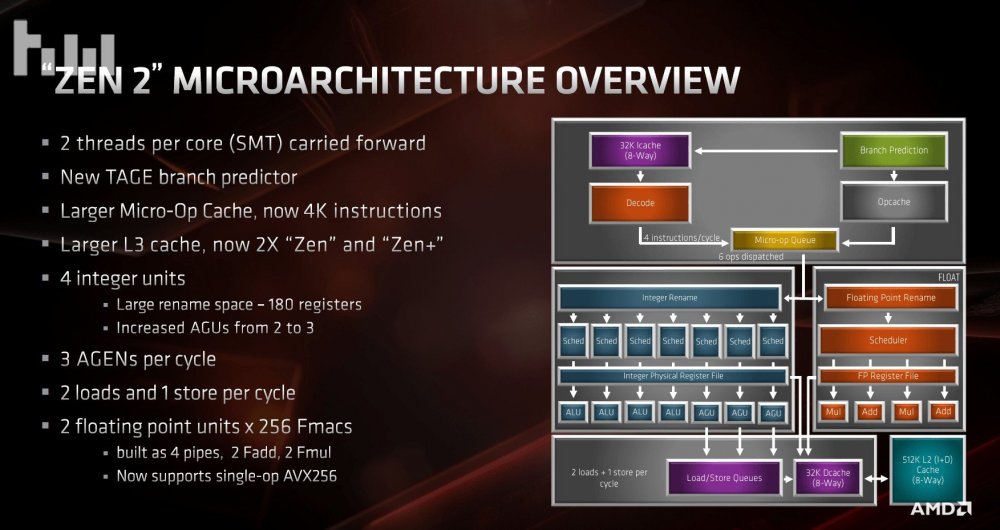

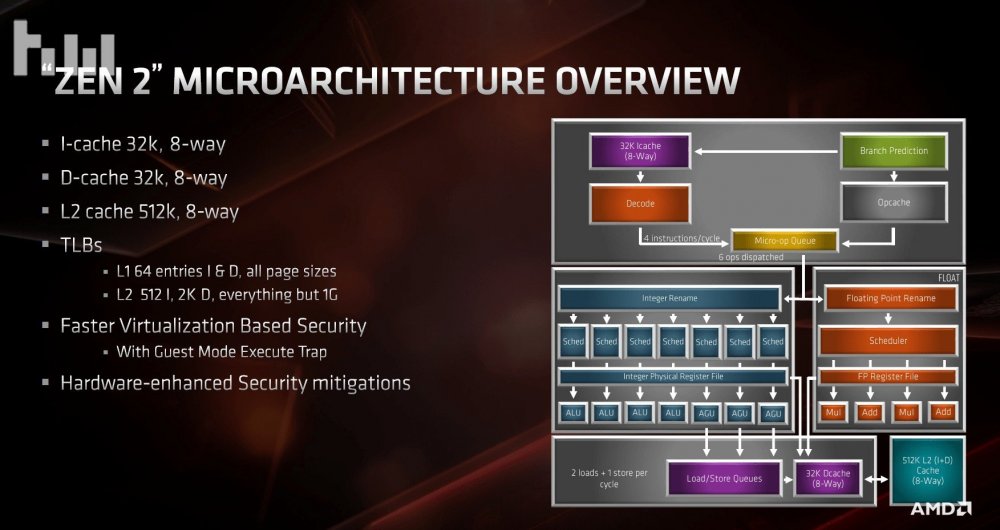

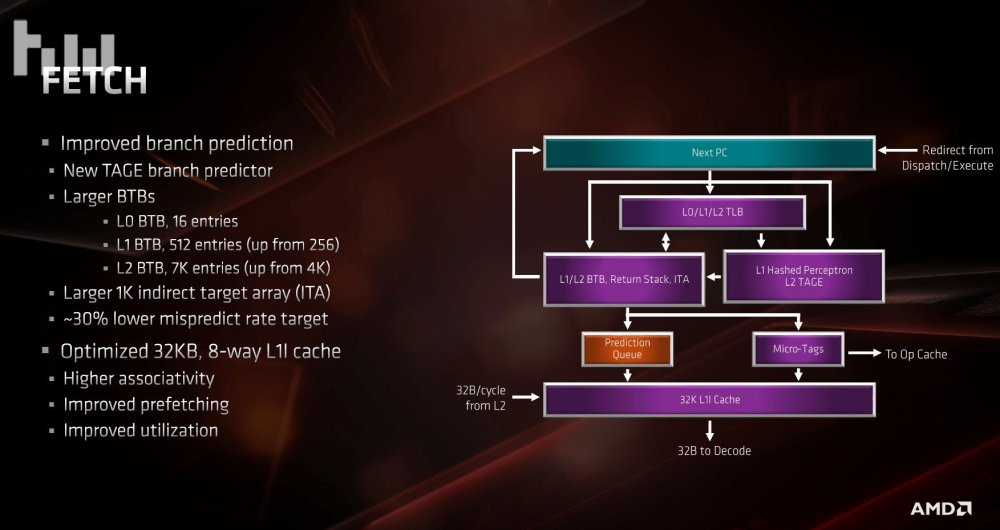

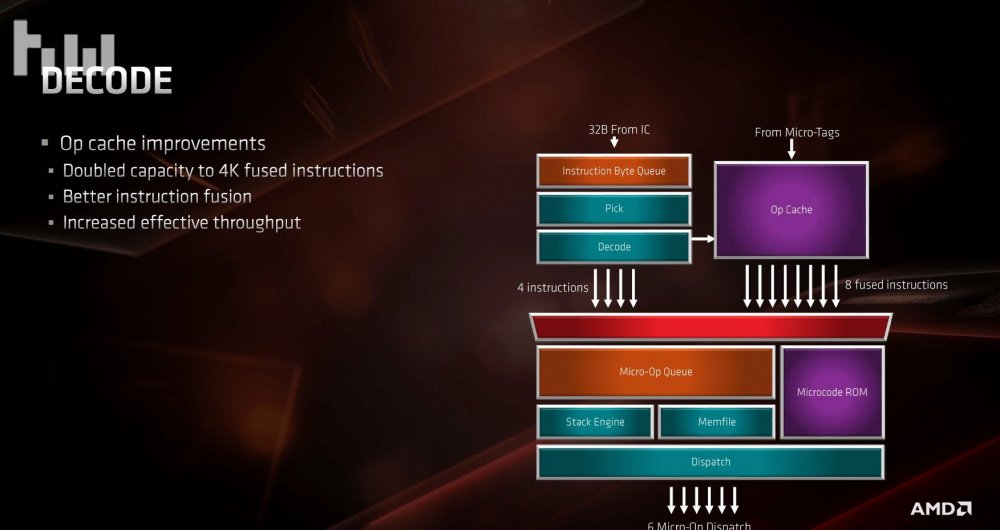

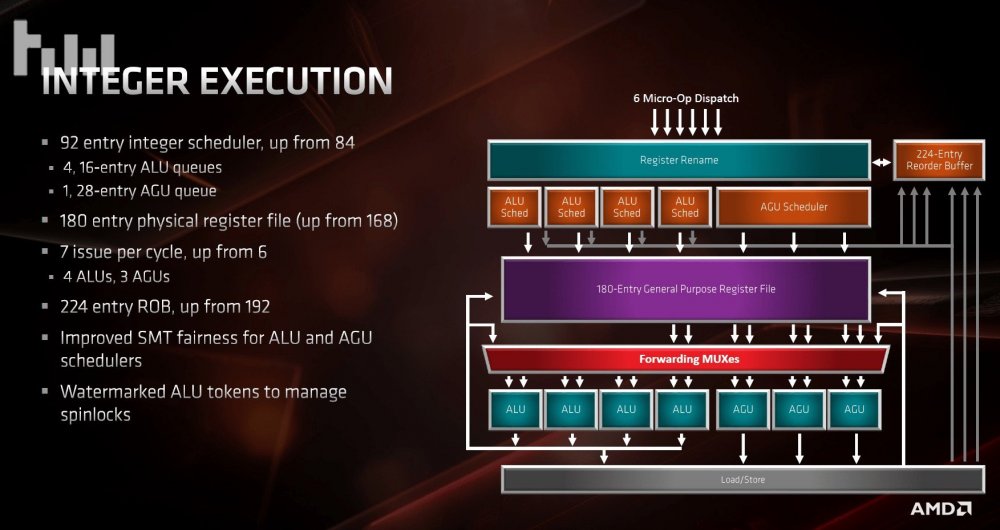

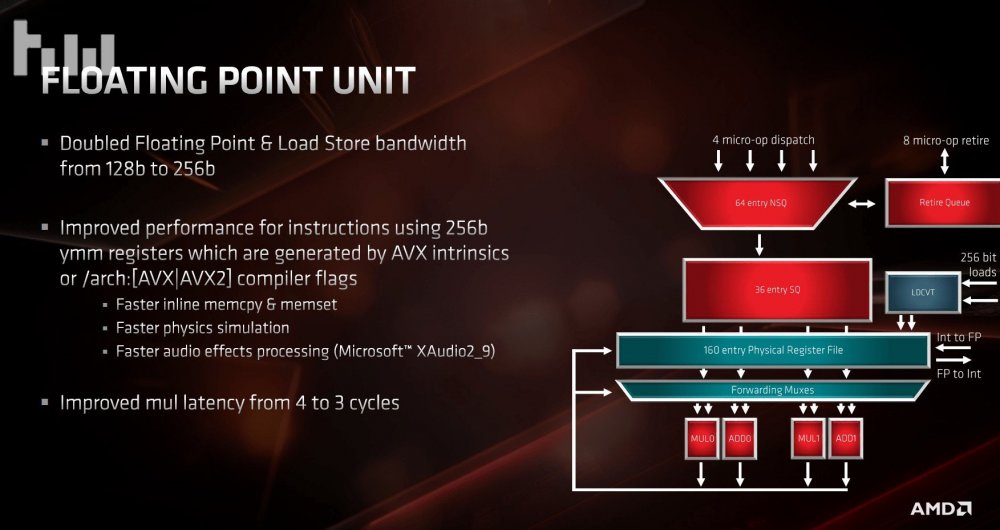

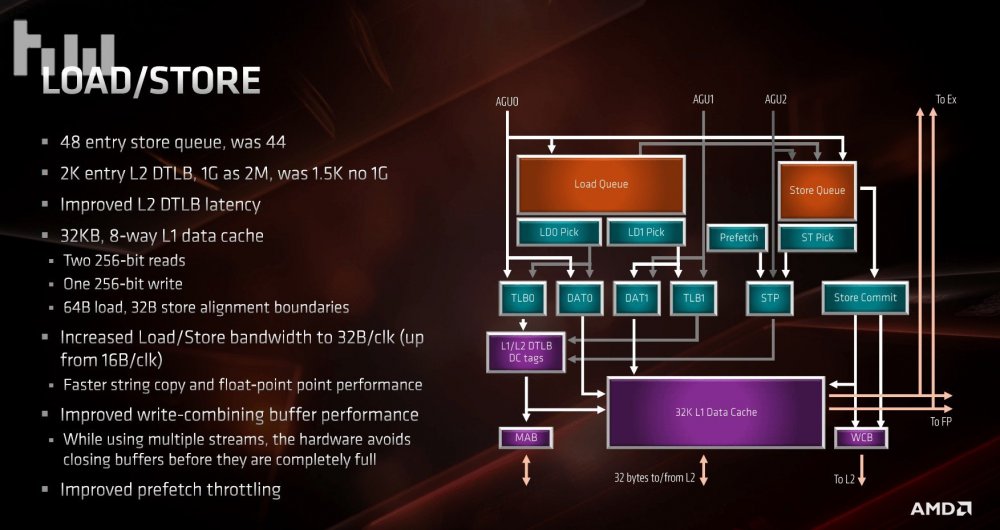

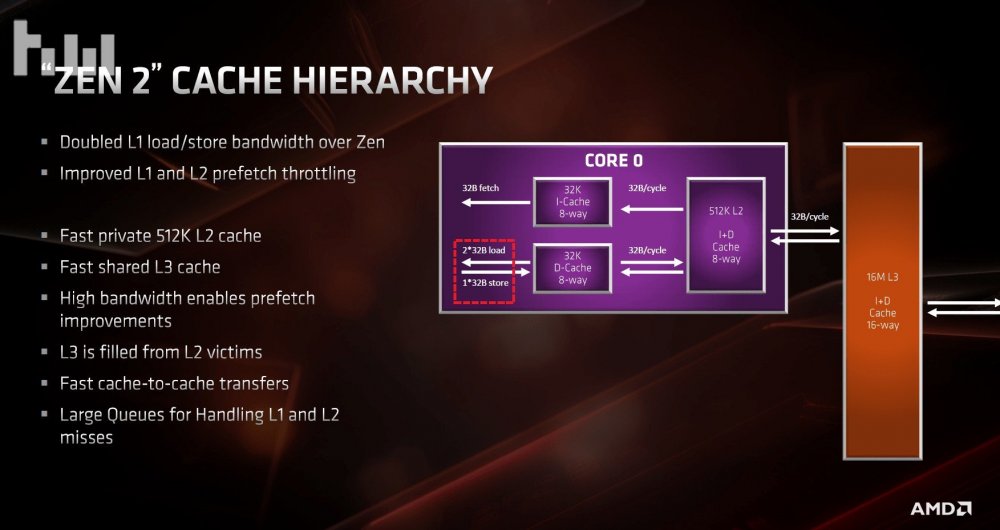

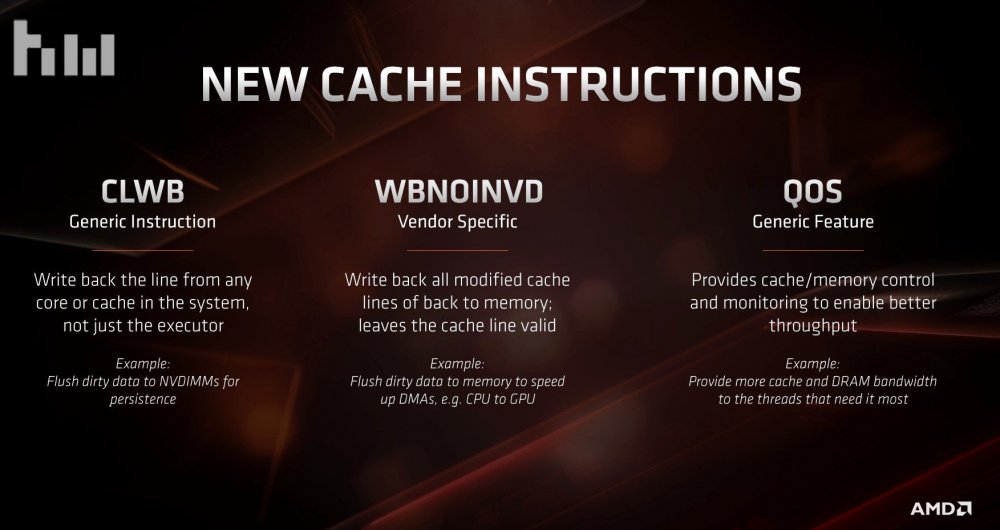

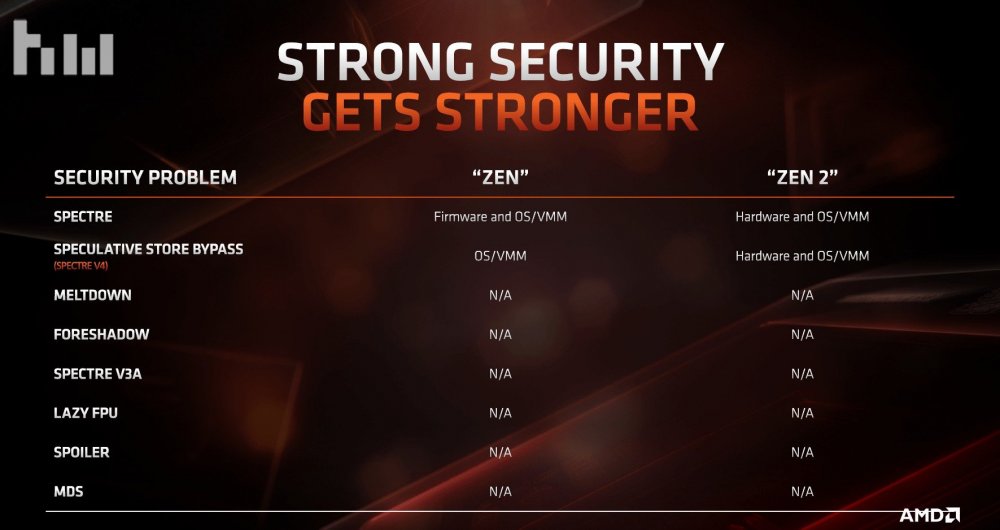

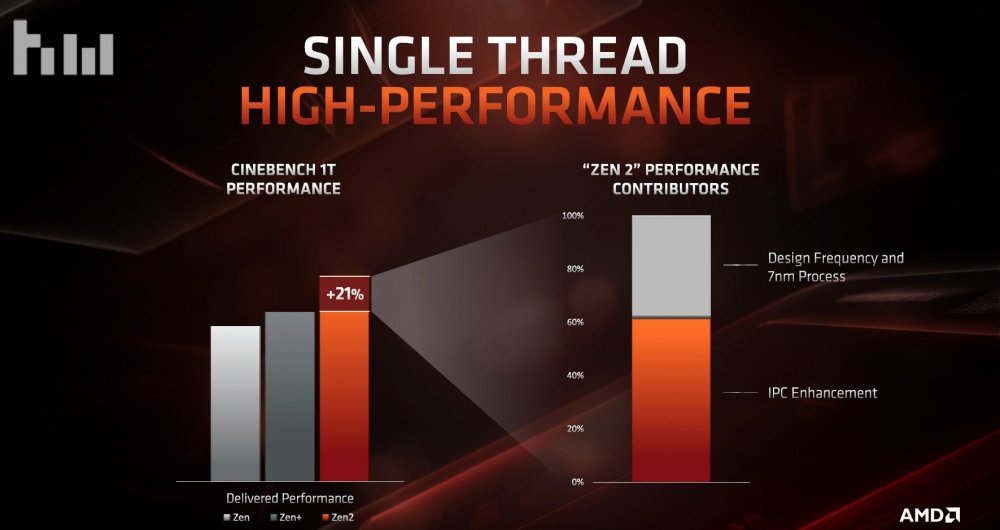

Enter Zen 2. Κατά τη διάρκεια της E3 η AMD μοιράστηκε με τον κόσμο περισσότερα στοιχεία για την αρχιτεκτονική της η οποία αλλάζει ριζικά από τις προηγούμενες με στόχο να ικανοποιήσει τις συνεχώς αυξανόμενες ανάγκες της αγοράς. Η AMD θεωρεί ότι ο αριθμός των πυρήνων έχει μεγάλη ζήτηση κάτι που 'συμπαρασέρνει' τη τοπική cache τους - και εδώ βλέπουμε μια AMD που αυξάνει και τα δύο αφού στο AM4 θα βρούμε ένα 16πύρηνο μοντέλο με 72MB συνολικής cache (Ryzen 9 3950X). Αυτό που αυξάνεται σημαντικά σε αυτή τη γενιά είναι η προσωρινή μνήμη των CPUs και η AMD αναφέρει πως είναι διπλάσια από τις προηγούμενες γενιές Zen, Zen+. Ο τομέας της ασφάλειας έχει ληφθεί υπόψιν με hardware mitigations στο εσωτερικό των επεξεργαστών, ένα σημαντικό θέμα που έγινε 'πρωτοσέλιδο' σε αρκετά media με αφορμή όμως chips της Intel, ένας τομέας όπου η AMD είχε αρκετή... ανοσία. Η δεύτερη σημαντικότερη αλλαγή μετά τον διπλασιασμό της cache είναι σίγουρα ο branch predictor και οι μικροβελτιώσεις που τον κάνουν να 'βλέπει' τις μελλοντικές εντολές πιο εύκολα και αποδοτικά - με λιγότερα ίσως mispredictions από το παρελθόν. Οι μονάδες επεξεργασίας ακέραιων και κινητής υποδιαστολής αριθμών έχουν υποστεί και αυτές σημαντικές αλλαγές από τη προηγούμενη γενιά και αυτό χάρη στη μετάθεση του uncore σε ξεχωριστό die όπως θα δούμε στη συνέχεια. Όσον αφορά την μονάδα κινητής υποδιαστολής ή αλλιώς την FPU, η AMD διπλασιάζει το FP και Load Store bandwidth από τα 128bit στα 256bit ενώ υπόσχεται και αύξηση των επιδόσεων σε λογισμικό που τρέχει AVX εντολές και είναι ένα στοιχείο που θα βοηθήσει τις κονσόλες στον πιο 'καθηλωτικό περιφερειακό ήχο' που διαφημίζεται. Πρακτικά έχουμε περισσότερες εντολές ανά clock και από εκεί προκύπτει το μεγαλύτερο μέρος του αυξημένου IPC των επεξεργαστών.

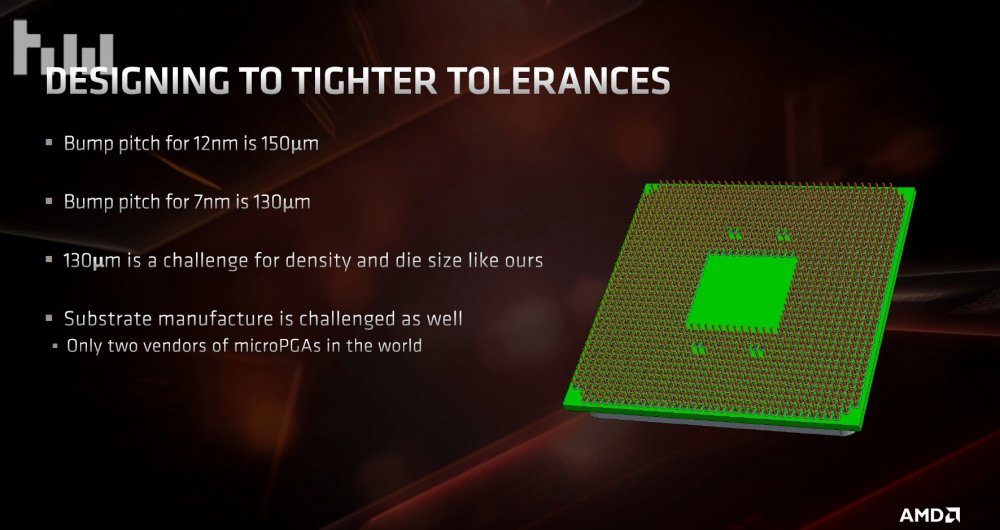

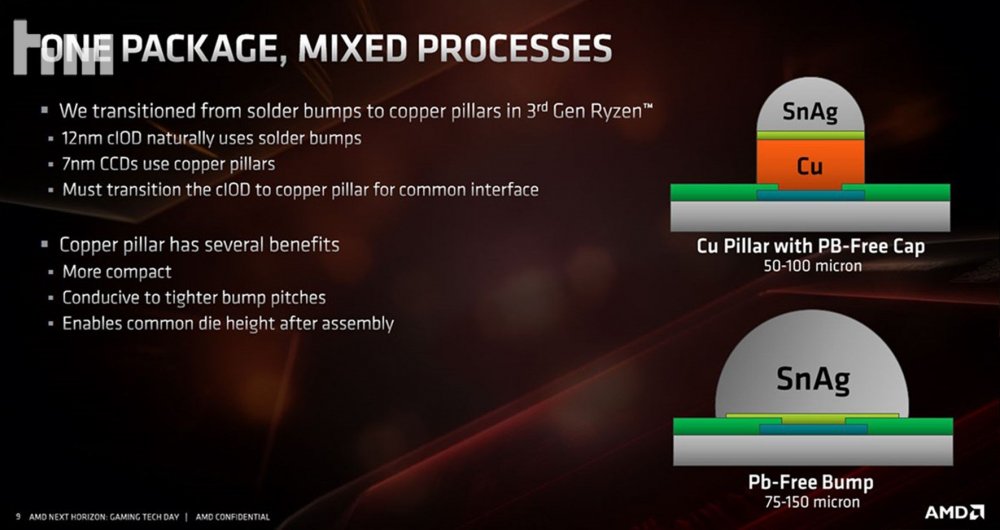

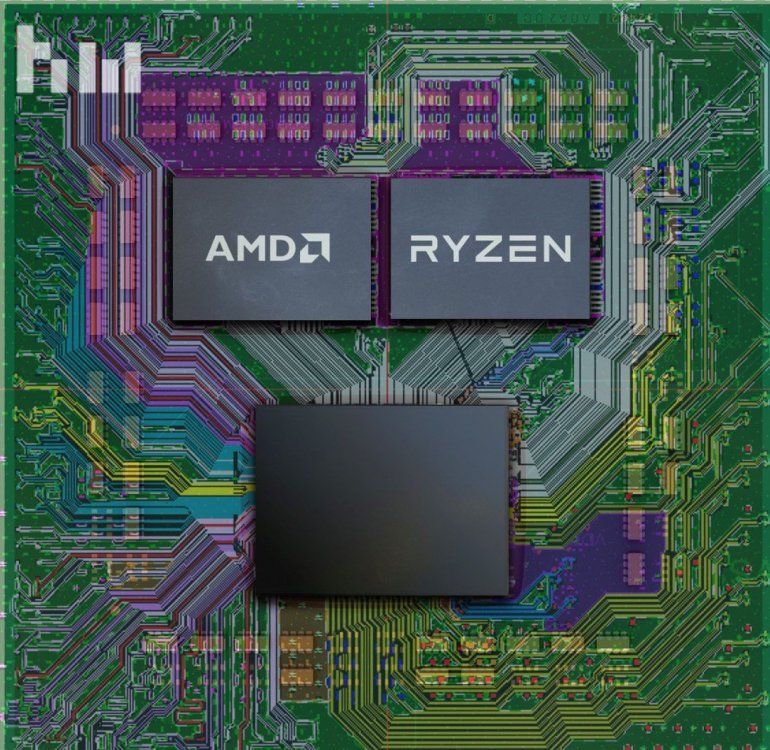

Οι πυρήνες έχουν διαφορετική λιθογραφία στα 7nm (TSMC) από 12nm του I/O die και της προηγούμενης γενιάς Ryzen. Σε αυτό το σημείο η AMD επισημαίνει κάτι σημαντικό. Ο τρόπος κατασκευής του ball grid array των core dies επάνω στο υπόστρωμα του PCB είναι ελαφρώς διαφορετικός από τη τελευταία φορά που είδαμε νέα Ryzen CPUs από την εταιρία. Τα CPU Core Dies σχεδιάζονται με ένα νέο τρόπο που περιλαμβάνει μικροσκοπικά χάλκινα bumps πάνω στα οποία βρίσκεται το μείγμα κασσίτερου και αργίλου, κοινώς η κόλληση που συνδέει τα dies με το υπόστρωμα του PCB. Η μέθοδος είναι κάτι εντελώς νέο στον χώρο και σύμφωνα με την AMD, οι ιδιότητες του χαλκού όσον αφορά την αντίσταση και τη μεταφορά των σημάτων είναι σε επιθυμητά επίπεδα και φέρει αρκετά πλεονεκτήματα σε σχέση με τη κόλληση και μερικών ακόμη στοιχείων που εφάπτονται άμεσα με το υπόστρωμα. Το I/O die από την άλλη διατηρεί την παραδοσιακή σχεδίαση με τη χρήση κόλλησης μαζί με ένα επιπλέον υλικό.

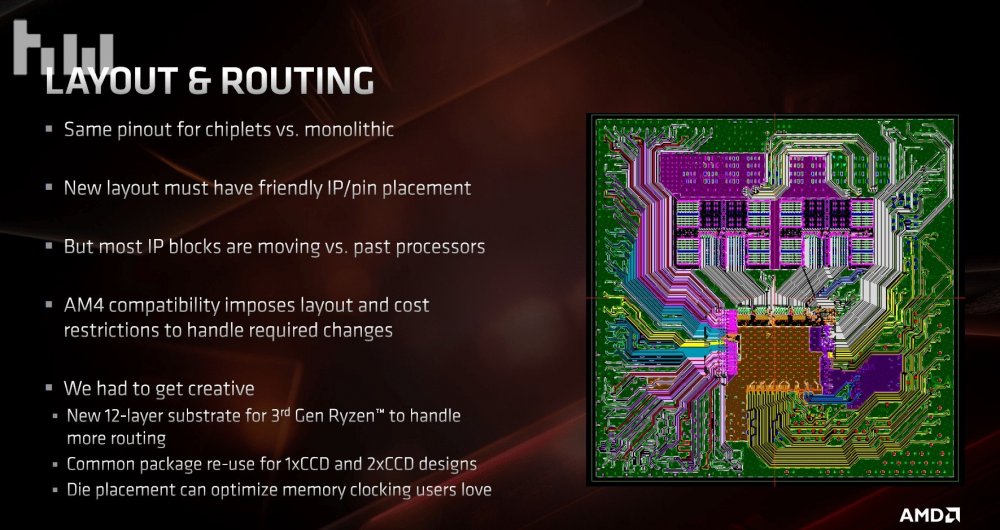

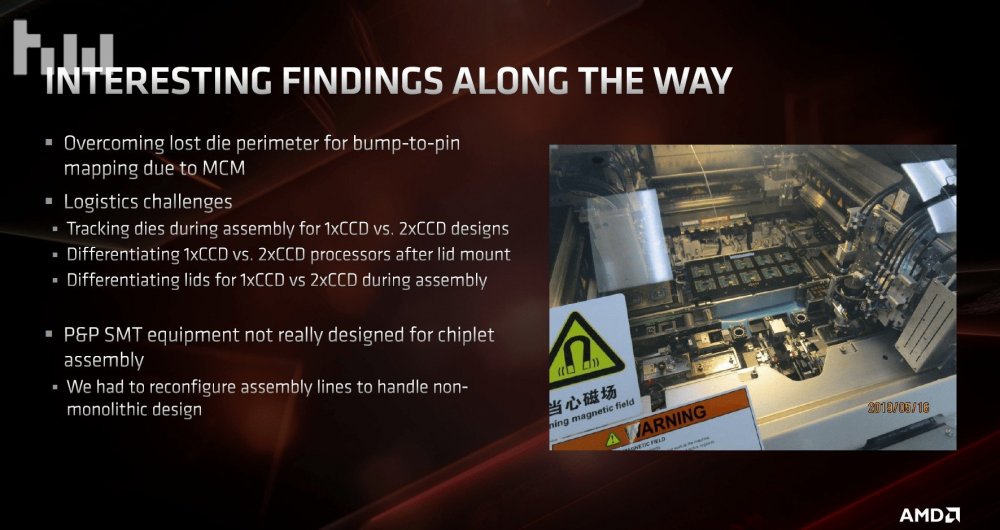

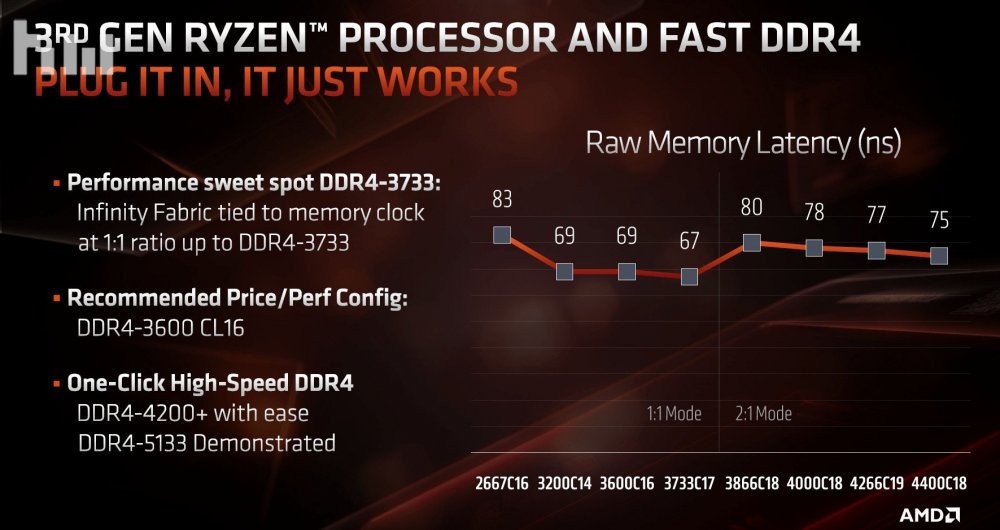

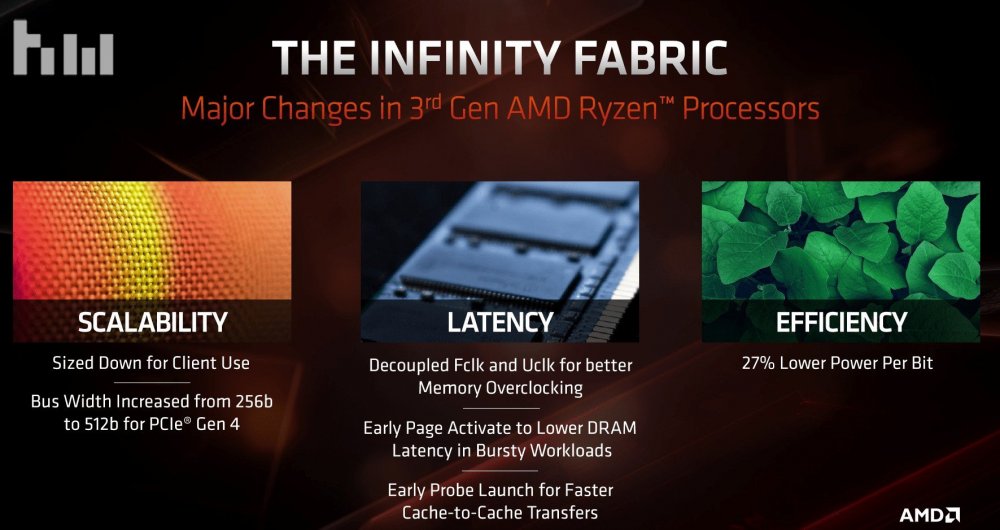

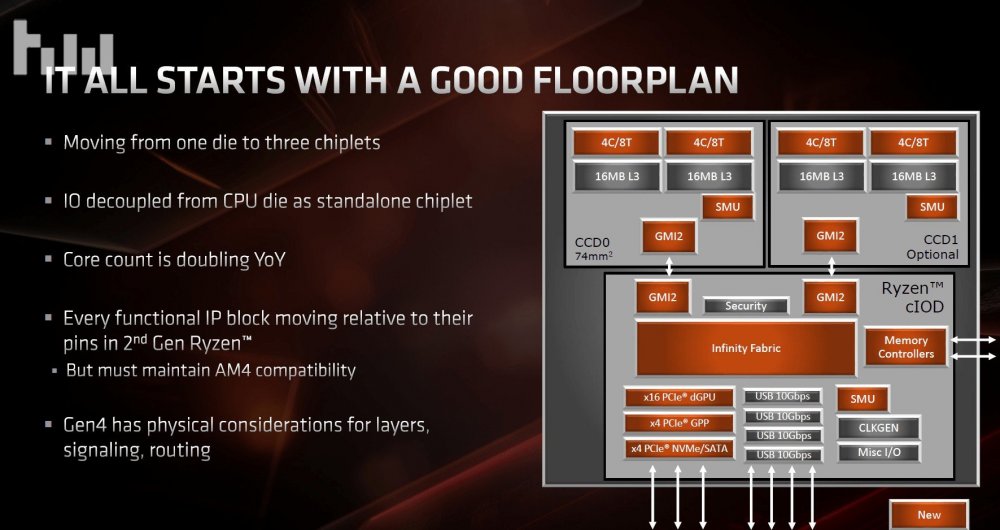

Η φετινή σχεδίαση των Ryzen 3000 αποτελείται από έως τρία chiplets όπως τα ονομάζει η AMD, με το ένα (ή τα δύο ανάλογα το μοντέλο που ελέγχουμε) να στεγάζει τους πυρήνες, τις τοπικές cache και τον δίαυλο Infinity Fabric για την επικοινωνία με το δεύτερο chiplet, το I/O die - που ενσωματώνει όλα τα υπόλοιπα υποσυστήματα όπως τους memory controllers, τον PCIe Gen 4.0 controller, και πλήθος I/O όπως τις USB των 10Gbps και τις SATA των 6Gbps που γίνονται route ανάλογα με το τι θα επιλέξει ο κατασκευαστής της μητρικής. Το I/O die μπορούμε να το χαρακτηρίσουμε και southbridge λόγω της ύπαρξης ελεγκτών όπως SATA και USB, κάτι που είδαμε και στις προηγούμενες γενιές Ryzen CPU. Το routing των chiplets όπως αναφέρει η AMD ήταν μια δύσκολη διαδικασία στη συγκεκριμένη γενιά καθώς θα πρέπει να ξεπεραστούν οι περιορισμοί του μικρού AM4 socket σε σχέση με κάποιο μεγαλύτερο όπως το SP3 των Threadripper όπου υπάρχει άφθονος χώρος για μικρές ή μεγάλες χάλκινες 'οδούς', ενώ παράλληλα αρκετά μηχανήματα για τη κατασκευή των chip θα έπρεπε να ρυθμιστούν κατάλληλα για να υποστηρίξουν τη 'μη-μονολιθική' σχεδίαση που εφαρμόστηκε σε αυτή τη γενιά. Έτσι η AMD τοποθέτησε στο substrate 12 συνολικά layers για να συνδέσει όλα τα components, ενώ η τοποθέτηση του I/O die προωθεί το overclocking των μνημών κάτι που ζητούσε η κοινότητα εδώ και καιρό. Ο τρόπος που το κάνει αυτό είναι διαχωρίζοντας το βασικό clock από τα Fclk και Uclk, το πρώτο έχει άμεση σχέση με τον PCIe ελεγκτή και λειτουργεί κατά μια έννοια σαν strap για να μην επιτρέψει την αύξηση στο 'ευαίσθητο' αυτό clock. Έτσι η νέα γενιά υπόσχεται ταχύτητες που θα φτάνουν και σε πολλές περιπτώσεις θα ξεπερνούν τα 4000MHz.

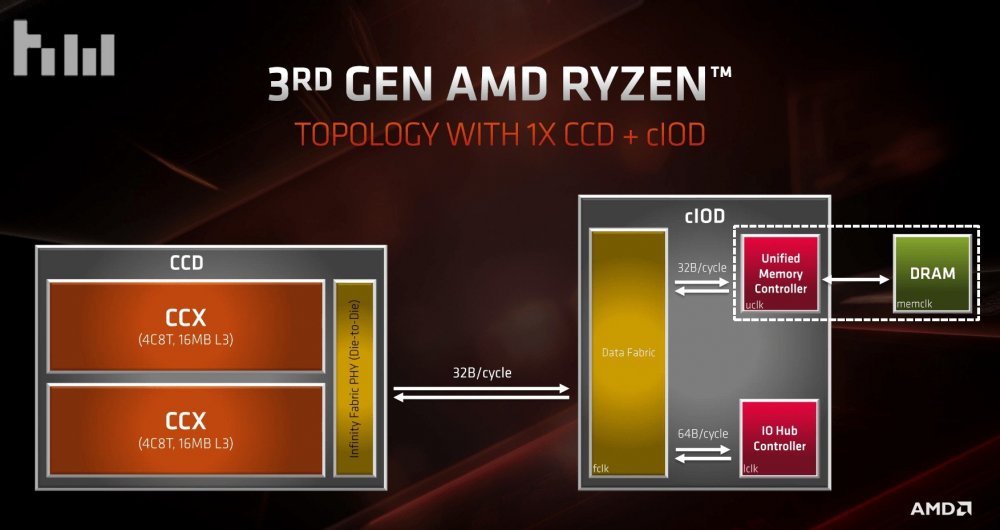

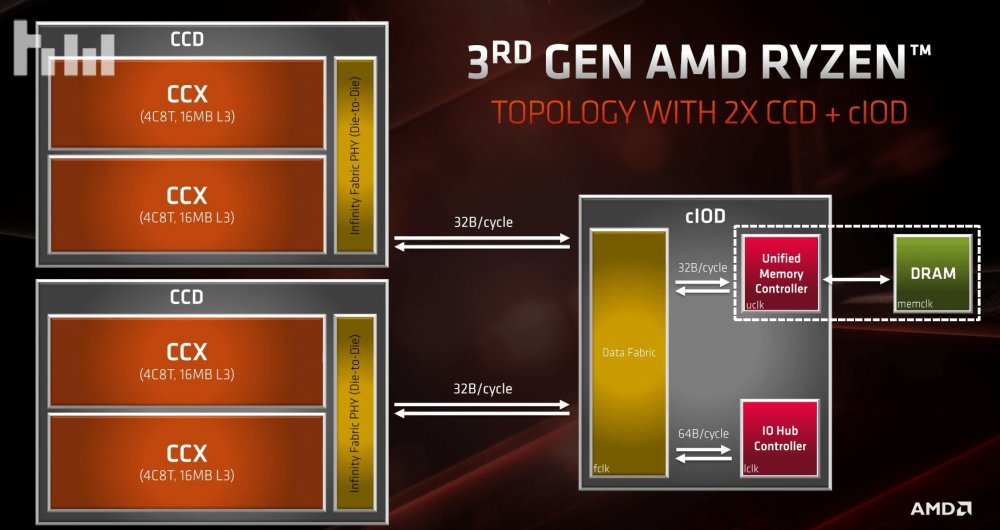

Το Core Complex σχεδιαστικά βαδίζει σε γνώριμα μονοπάτια και κάθε ένα από αυτά περιλαμβάνει τέσσερις φυσικούς πυρήνες με αποκλειστικές L2 και L3 cache των 512KB και 4MB αντίστοιχα, ενώ η L3 αναφέρεται ως 'slice' σε κάθε core αφού γνωρίζουμε ότι διαμοιράζει δεδομένα προς όλους τους πυρήνες του συμπλέγματος. Έτσι η L3 βρίσκεται στα 16MB ανά CCX (Core Complex) και αυτό με τη σειρά του αποτελεί μέρος ενός CCD (CPU Core Die). Το τελευταίο περιλαμβάνει πλέον δύο CCXs με 8 συνολικά πυρήνες (16T), 32MB cache και τον δίαυλο Infinity Fabric για τη σύνδεση με το γειτονικό I/O chiplet. Η σύνδεση μέσω αυτού του διαύλου προωθεί 32 Byte ανά κύκλο ρολογιού και εδώ σημειώνεται ότι το αρχικό clock δίνεται από oscillator που βρίσκεται στο I/O die, άλλο ένα στοιχείο που βρίσκουμε μόνο σε chipsets μητρικών εδώ και χρόνια, ή αλλιώς το southbridge που αναφέραμε νωρίτερα. Η AMD μας δείχνει μαζί ένα πιο μεγάλο σε μέγεθος σχέδιο που περιλαμβάνει δύο CCX αναφέροντας πως αυτά συνδέονται επάνω στο Ι/Ο chiplet οπότε στη προκειμένη περίπτωση βλέπουμε την 'κάτοψη' του μεγάλου μοντέλου, Ryzen 9 3950X.

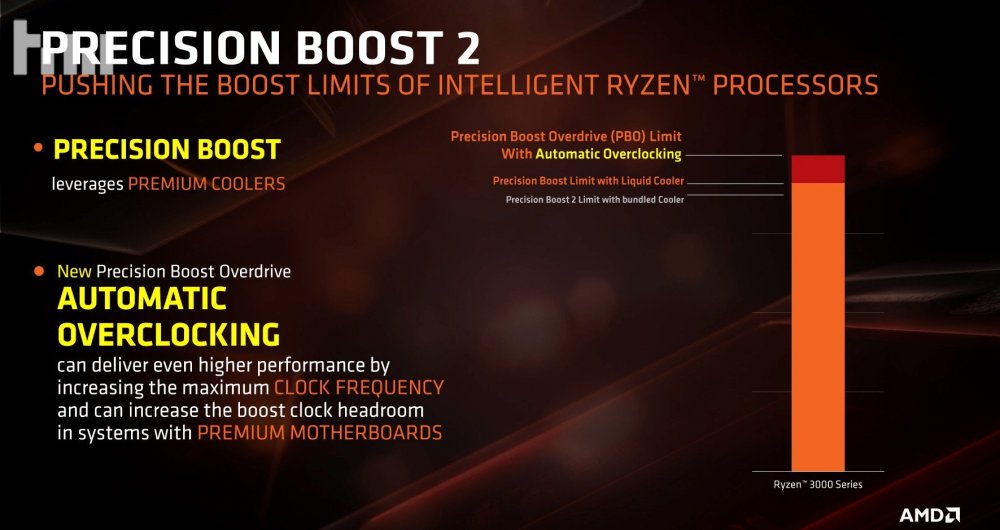

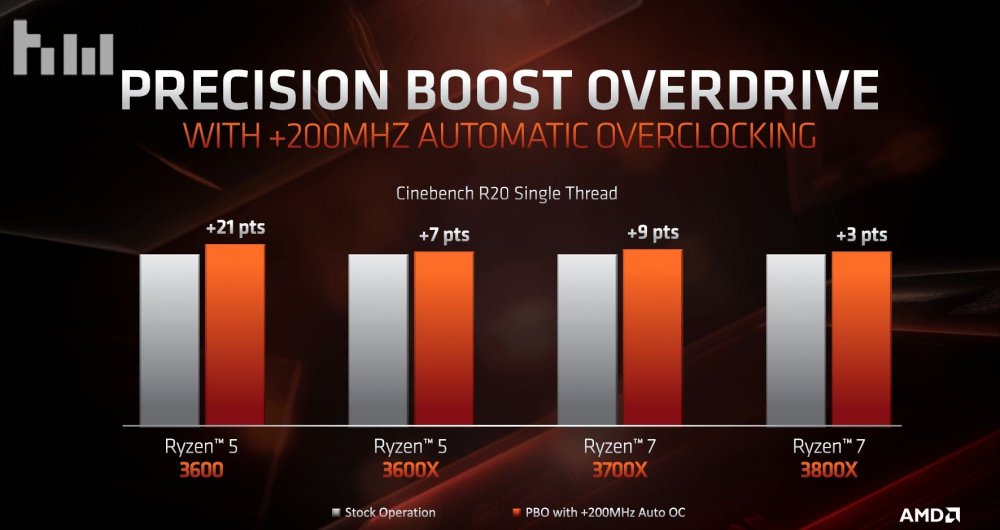

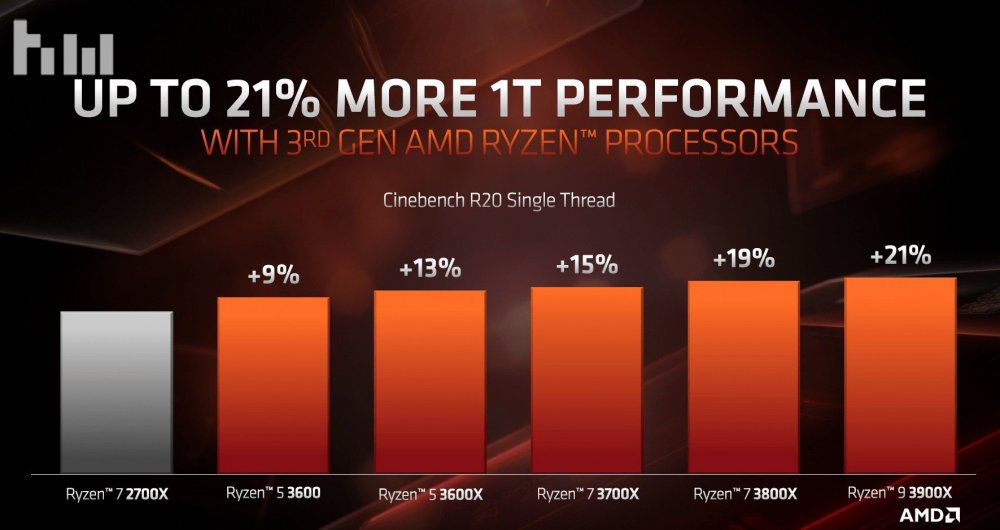

Φεύγοντας από τη σχεδίαση και το εσωτερικό των νέων chips περνάμε σε ένα εξίσου βαρυσήμαντο κεφάλαιο, αυτό του Precision Boost που μένει στη δεύτερη γενιά με μερικές βελτιώσεις και ουσιαστικά ενεργοποιεί το αυτόματο overclocking του επεξεργαστή - αλλά παρέα με μια premium μητρική που θα έχει το απαραίτητο κύκλωμα τροφοδοσίας για να υποστηρίξει την επιλογή. Φυσικά μιλάμε για κάποια X series μητρική όπως αυτές με το νέο X570 chipset, ενώ το feature του Precision Boost Overdrive θα γίνει πιο ξεκάθαρο αφού στις Χ370 και X470 βρισκόταν βαθιά χωμένο στο BIOS, με μερικές εξαιρέσεις στη πλατφόρμα των Threadripper σε μερικούς motherboard vendors. Η αύξηση στις επιδόσεις θα είναι μετρήσιμη κατά την AMD και γι' αυτόν τον λόγο παρουσιάζει τις επιδόσεις που θα κερδίσουν όσοι πάρουν στα χέρια τους κάποιον επεξεργαστή Ryzen τρίτης γενιάς. Το PBO στις περισσότερες περιπτώσεις (ανάλογα με το chip) θα αυξήσει τα ρολόγια κατά 200MHz στον επεξεργαστή όμως η σταθερότητα και η διατήρηση αυτών των χρονισμών εξαρτάται αρκετά από την ψύκτρα που έχουμε εγκατεστημένη στο σύστημά μας.

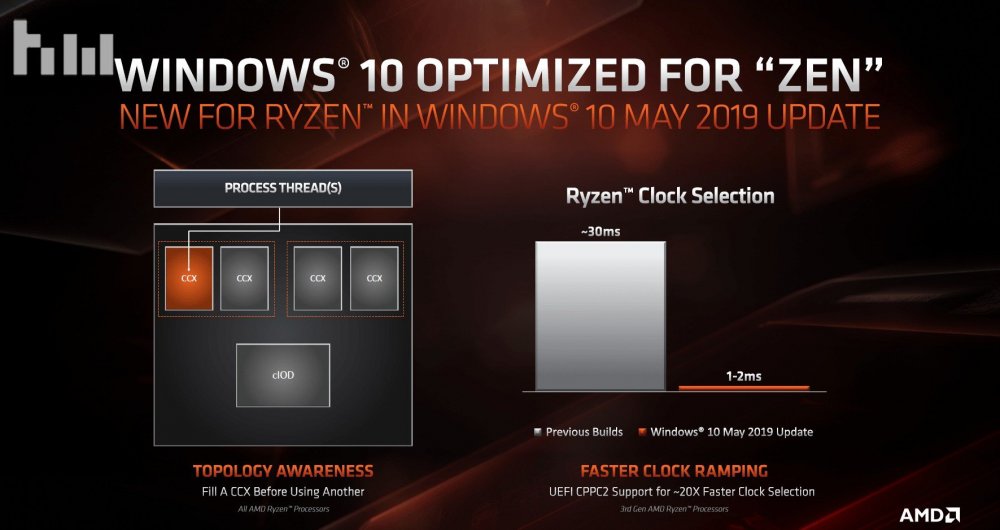

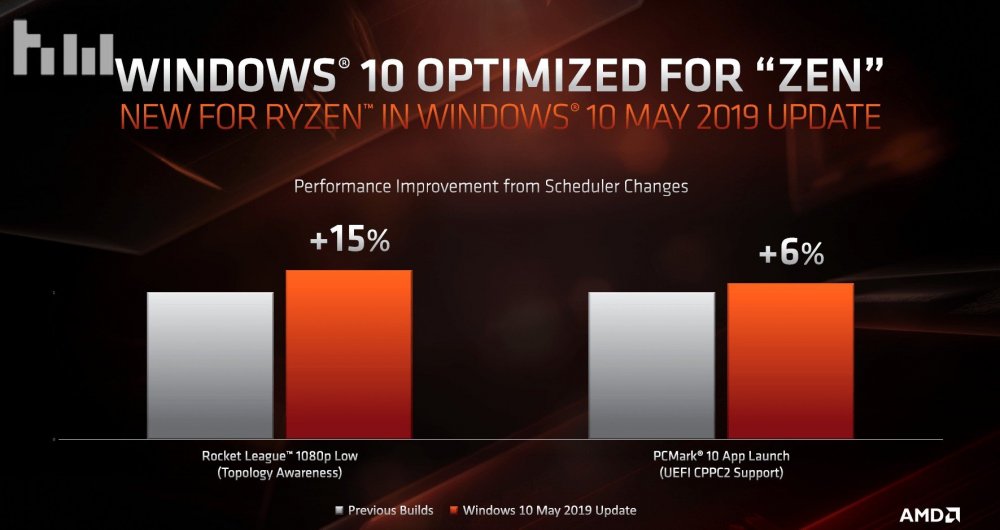

Στην software πλευρά, ή αλλιώς στα υψηλότερα στρώματα του λογισμικού όπως στα Windows 10 βλέπουμε μια αισθητή κίνηση της AMD να βελτιώσει πράγματα που μέχρι πρότινος αποτελούσαν περιοριστικό παράγοντα, με σημαντικότερο τον scheduler του δημοφιλούς λειτουργικού συστήματος αλλά και τον τρόπο που επιλέγει το κατάλληλο clock ανάλογα με το workload. Το 'clock selection' δηλαδή θα παίρνει σημαντικά λιγότερο χρόνο για να πραγματοποιηθεί (1-2ms) έναντι 30ms και όλα αυτά με την αναβάθμιση στη νεότερη Build 1903 των Windows 10, ή αλλιώς, το Update του Απριλίου. Αυτή η αλλαγή θα γίνει αισθητή μόνο σε όσους μεταβαίνουν στη νέα πλατφόρμα οπότε όσοι αναβαθμίσετε καλό θα είναι να πραγματοποιήσετε μια καθαρή εγκατάσταση των Windows 10 με την πιο πρόσφατη build. Όσον αφορά τους παλιότερους επεξεργαστές (Ryzen 2000 και πίσω), τα Windows πλέον θα προσπαθούν να μη μοιράζουν τις εφαρμογές σε πολλά CCX's (scheduler optimizations) μιας και η μεταξύ τους επικοινωνία μπορεί να έχει σημαντικό hit στις επιδόσεις λόγω του υψηλού latency. Αυτό όμως δε σημαίνει ότι η κίνηση αυτή θα μειώσει και την κατανάλωση των chips αφού θα πρέπει να υπολογίσουμε και την ενέργεια που καταναλώνει το Infinity Fabric για την επικοινωνία με το chiplet και σε αυτή τη γενιά περιμένουμε να τρέχει συνέχεια σε υψηλά ποσοστά.

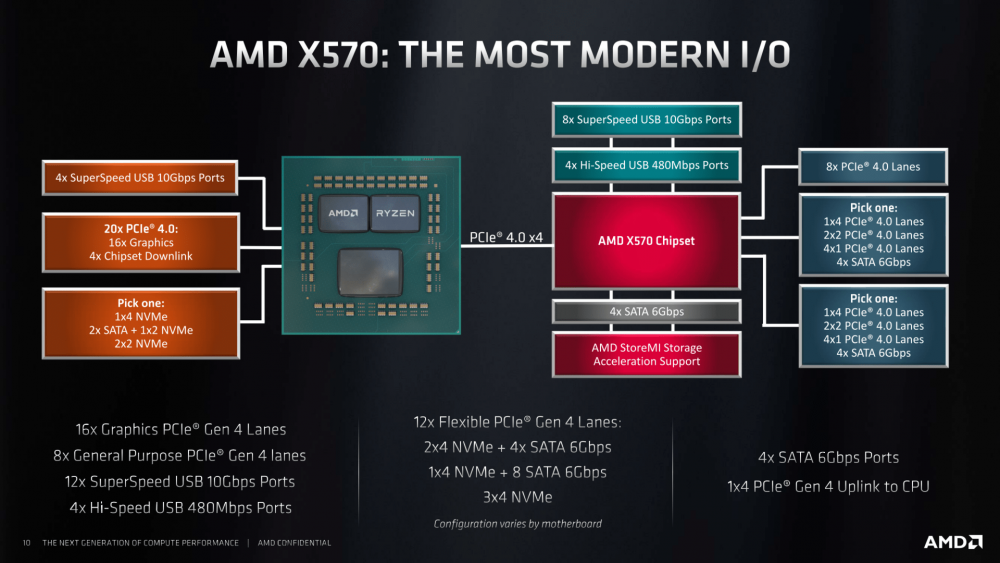

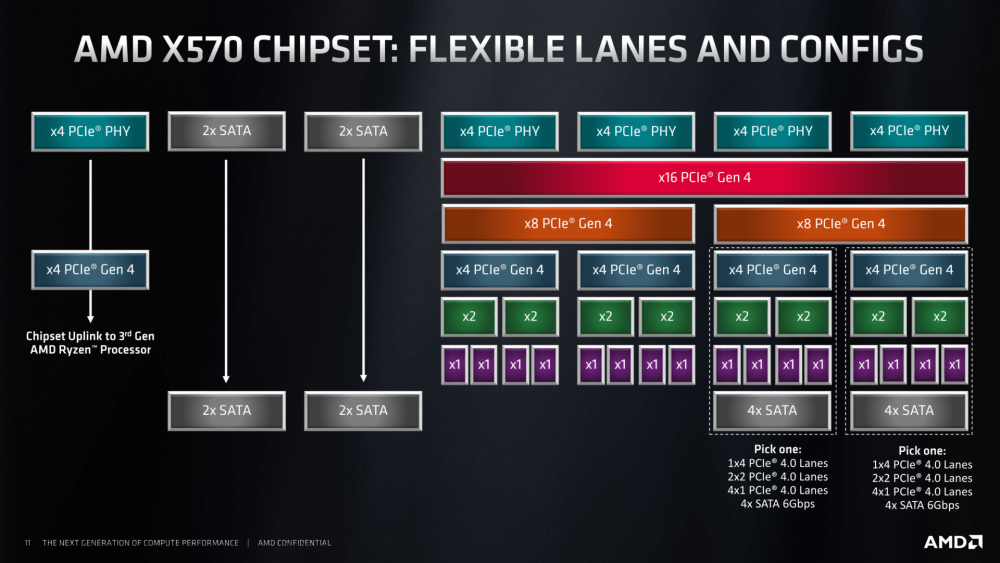

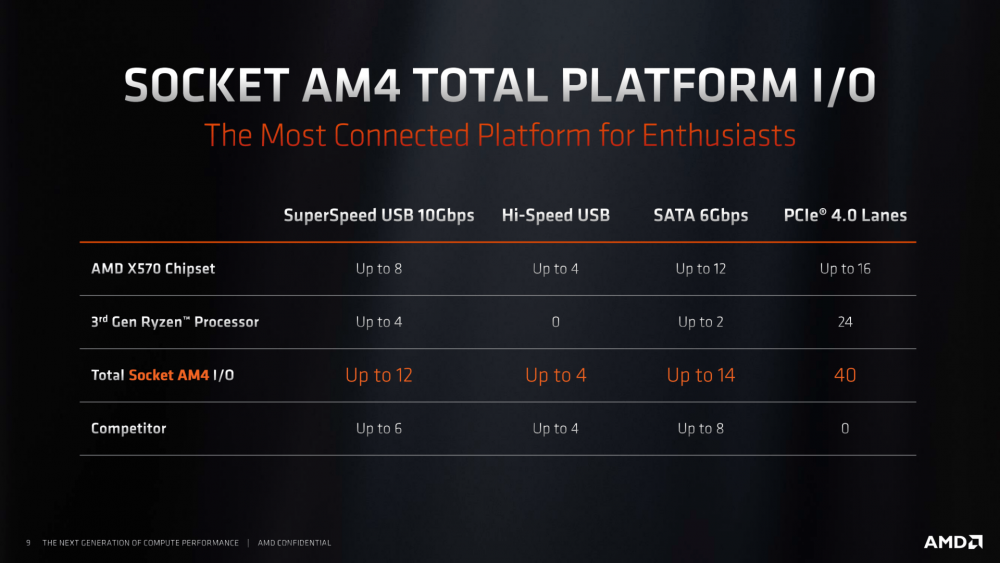

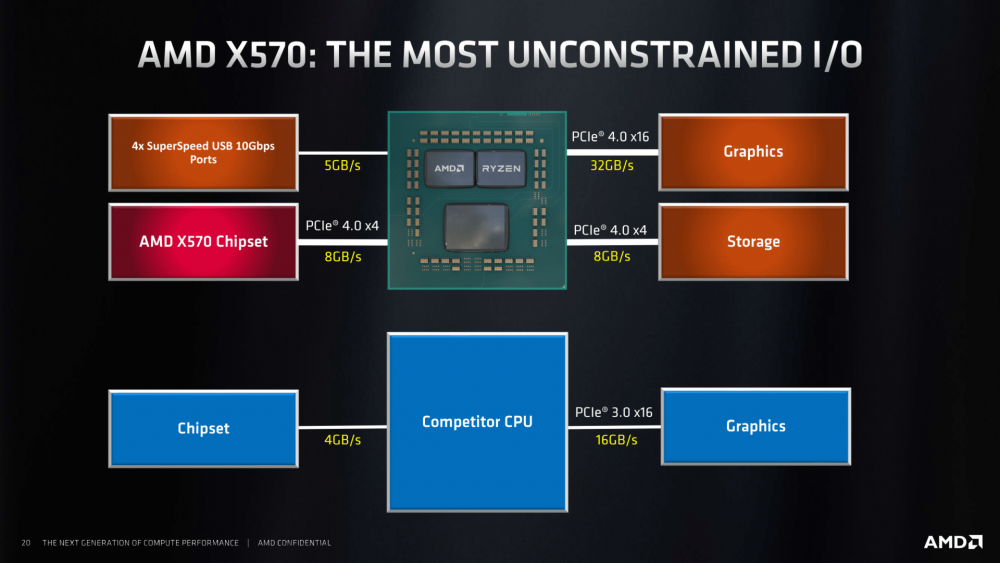

Οι Ryzen 3000 θα είναι οι πρώτοι επεξεργαστές της αγοράς που θα ενσωματώνουν τον γρήγορο δίαυλο επικοινωνίας PCIe Gen 4.0 και τον χρησιμοποιούν εκτενώς για τη σύνδεση και με το X570 chipset το οποίο αξίζει να πούμε πως φέρει και δικές του PCIe Gen 4.0 γραμμές για διάφορες περιφερειακές συσκευές. Όπως είπαμε παραπάνω από το I/O die φεύγουν διάφορες συσκευές όπως 4x USB 3.2 των 10Gbps που γίνονται route στη μητρική, 20 PCIe Gen 4.0 lanes 16 εκ των οποίων συνδέονται με το πρώτο συνήθως PCIe slot για GPUs ενώ τα 4 lanes που περισσεύουν συνδέουν τον επεξεργαστή με το X570 chipset. Στις storage επιλογές που τρέχουν από τον επεξεργαστή έχουμε τρεις επιλογές. Είτε τη χρήση ενός NVMe σε x4 mode, είτε ενός συνδυασμού δύο SATA + NVMe με τη μισή ταχύτητα (x2) ή τέλος, δύο NVMe SSD drives με τη μισή ταχύτητα που λόγω της νέας έκδοσης του διαύλου (Gen 4) οι ταχύτητες δεν αναμένονται ιδιαίτερα... χαμηλές. Σημαντική είναι η διατήρηση του διαύλου επικοινωνίας CPU + Chipset σε Gen 4.0 mode κάτι που υπόσχεται ακόμα μεγαλύτερες ταχύτητες μεταξύ των δύο αυτών υποσυστημάτων.

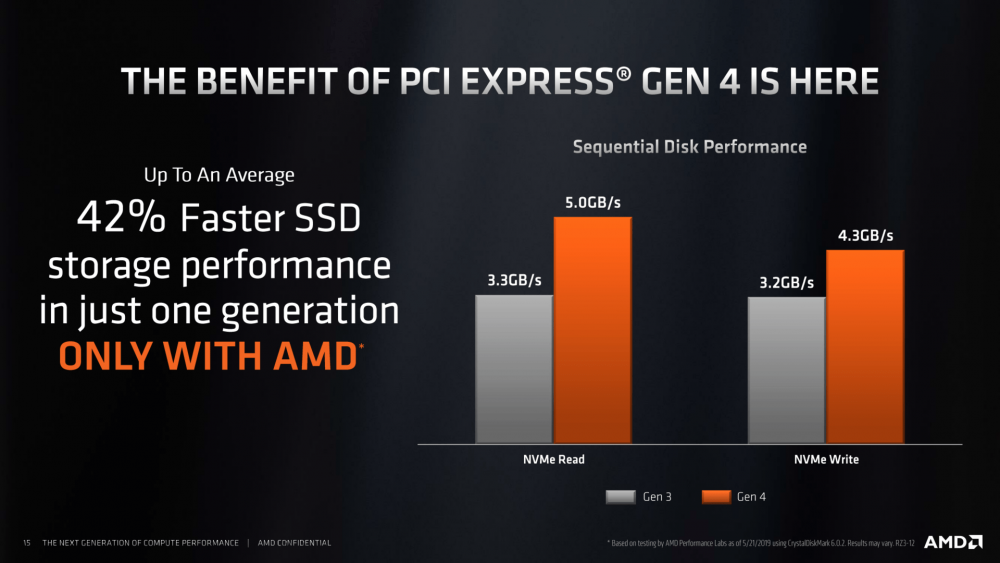

Στη πλευρά του chipset έχουμε πλήθος συσκευών όπως 8 USB 3.2 10Gbps και 4 x Hi-Speed USB 2.0 θύρες με ρυθμό διαμεταγωγής που αγγίζει τα 480Mbps. Από το ίδιο υποσύστημα (X570) φεύγουν και 4 SATA ports που γίνονται route στη συνήθη θέση των μητρικών υποστηρίζοντας το AMD StoreMI Storage Acceleration. Έτσι μπορεί να έχουμε 2x NVMe drives στη πλήρη ταχύτητα και 4 SATA III 6Gbps ή στη περίπτωση που δεν έχουμε κανένα μέσο αποθήκευσης SATA να τοποθετήσουμε τρεις NVMe στη πλήρη ταχύτητα, εάν φυσικά η μητρική το επιτρέπει. Βέβαια οι διαθέσιμες επιλογές δεν τελειώνουν εκεί αφού η λίστα των γραμμών συνεχίζεται. Το X570 θα δίνει και άλλες 8x PCIe γραμμές γενικής χρήσης που θα ενσωματώνονται στις θύρες επέκτασης της μητρικής (PCIe slots) ενώ οι κατασκευαστές μητρικών είναι ελεύθεροι να επιλέξουν αυτό που καλύπτει καλύτερα τις ανάγκες των αγοραστών τους όπως αναφέρει το σχετικό πλαίσιο στα slides της εταιρίας. Τα οφέλη με τη χρήση του νέου διαύλου είναι σημαντικά αλλά μόνο στη περίπτωση του storage αφού οι κάρτες γραφικών δε μπορούν να πλησιάσουν στα όρια του bandwidth ακόμα και της Gen 3.0 έκδοσης. Στο storage λοιπόν έχουμε ήδη δει την ύπαρξη αρκετά γρήγορων drives με Phison controllers και NAND Flash της Toshiba και εκεί είναι που στέκεται η AMD.

Τα μοντέλα των Ryzen 3000 θα είναι συνολικά 7 μαζί με τους APUs, ωστόσο τη νέα αρχιτεκτονική Zen 2 θα φέρουν μόνο οι 5 εξ' αυτών. Η συμβατότητα προς τα πίσω θα φτάνει μέχρι και σε επιλεγμένες B350 μητρικές, όμως είναι σημαντικό να τονίσουμε ότι πιθανόν τα μελλοντικά patches που θα διαθέσει η εταιρία να μη περάσουν ποτέ σε αυτές τις μητρικές σε αντίθεση με τις 400 Series (B450 & X470) όπου θα δούμε πλήρη υποστήριξη και κάλυψη με τα απαραίτητα patches στο μέλλον. Η προγραμματισμένη ημερομηνία κυκλοφορίας είναι η 7η Ιουλίου του 2019 και έως τότε θα έχουμε περισσότερο υλικό.

Slides @AMD

amd, architecture, L3 cache , Infinity Fabric, 2019, zen 2, ryzen 3000, cache

Nickzzz

Ενδιαφέροντα όσα κάνει η AMD για να ξεπεράσει διάφορα προβλήματα που θα είχε αν πήγαινε με κλασσική σχεδίαση.

Και η ιδέα των chiplets φαίνεται να πετυχαίνει για την ώρα.

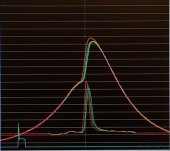

Ωραίο και το 32 MB L3 ανά CCX αν και μάλλον μπήκε για να μειώσει κάπως το συνολικό latency; Γιατί φαίνεται σαν πισωγύρισμα να φεύγει ο memory controller δίπλα από τους πυρήνες και να πηγαίνει στο i/o die. Και θα προσθέτει και latency αφού πάλι με το ζόρι πάμε κάτω από 70 ns.![]()

Αν και έτσι έκκεντρα που είναι τώρα πια τα πράματα, αναρωτιέμαι πως θα γίνεται σωστή ψύξη, που είχαμε συνηθίσει στο κέντρο την μεγάλη παραγωγή θερμότητας.

2 βδομάδες ακόμα και βλέπουμε. ![]()