Η JEDEC αποκαλύπτει τα specs για τις LPDDR4

Η [B]JEDEC [/B]αποκάλυψε πληροφορίες για τις νέες μνήμες χαμηλής κατανάλωσης που θα βρουν στέγη σε φορητές συσκευές. Η [B]JEDEC [/B]αποκάλυψε πληροφορίες για τις νέες μνήμες χαμηλής κατανάλωσης που θα βρουν στέγη σε φορητές συσκευές.

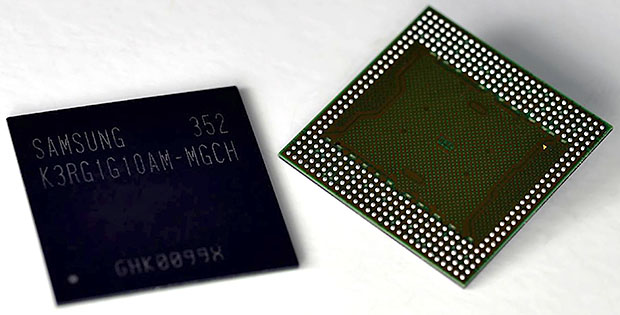

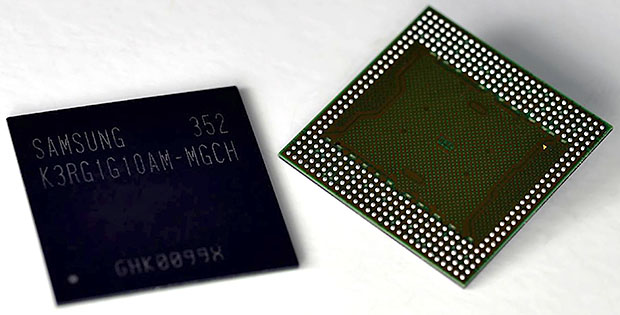

Ο γνωστός οργανισμός ανάπτυξης ανοικτών στάνταρ JEDEC ανακοίνωσε τα χαρακτηριστικά των μνημών χαμηλής κατανάλωσης Low Power Double Data Rate 4 (LPDDR4) τα οποία ενδείκνυται για χρήση σε φορητές συσκευές, όπου η κατανάλωση ενέργειας αποτελεί σημαντικό παράγοντα για την αύξηση της αυτονομίας. Σύμφωνα με τα specs, οι μνήμες θα έρχονται σε dual channel και το I/O throughput τους αγγίζει τα 3200 MT/s, ανεβαίνοντας μέχρι τα 4266 MT/s. Οι μνήμες λειτουργούν στα 1.1V (από 1.2v που είναι το επίσημο για τις desktop DDR4).

Παράλληλα έχουν γίνει μεγάλα βήματα στην περαιτέρω μείωση της κατανάλωσης με το βελτιωμένο I/O signaling που απαιτεί μόλις 367 έως 440mV το οποίο είναι σχεδόν 50% χαμηλότερο από τις αντίστοιχες LPDDR3. Τέλος, για την κατανόηση των αλλαγών,η JEDEC θα φιλοξενήσει το LPDDR4 Workshop στην Santa Clara, CA στις 23 Σεπτεμβρίου, 2014.

Κύρια χαρακτηριστικά:

Ο γνωστός οργανισμός ανάπτυξης ανοικτών στάνταρ JEDEC ανακοίνωσε τα χαρακτηριστικά των μνημών χαμηλής κατανάλωσης Low Power Double Data Rate 4 (LPDDR4) τα οποία ενδείκνυται για χρήση σε φορητές συσκευές, όπου η κατανάλωση ενέργειας αποτελεί σημαντικό παράγοντα για την αύξηση της αυτονομίας. Σύμφωνα με τα specs, οι μνήμες θα έρχονται σε dual channel και το I/O throughput τους αγγίζει τα 3200 MT/s, ανεβαίνοντας μέχρι τα 4266 MT/s. Οι μνήμες λειτουργούν στα 1.1V (από 1.2v που είναι το επίσημο για τις desktop DDR4).

Παράλληλα έχουν γίνει μεγάλα βήματα στην περαιτέρω μείωση της κατανάλωσης με το βελτιωμένο I/O signaling που απαιτεί μόλις 367 έως 440mV το οποίο είναι σχεδόν 50% χαμηλότερο από τις αντίστοιχες LPDDR3. Τέλος, για την κατανόηση των αλλαγών,η JEDEC θα φιλοξενήσει το LPDDR4 Workshop στην Santa Clara, CA στις 23 Σεπτεμβρίου, 2014.

Κύρια χαρακτηριστικά:

- Two-channel architecture

- Internal Vref supplies for CA and DQ

- Data Bus Inversion (DBI-DC)

- ODT for CA and DQ

- I/O throughput: 3200 MT/s, rising to 4266 MT/s

- Signaling voltage: 367mV or 440mV

- Operating voltage: 1.1V

- Pre-fetch size: 32B per channel

- Topology: Point to point, PoP, MCP

- Max I/O capacitance: 1.3pF

- Write leveling

- 6-pin SDR CA bus CA training (12 pins per two channels)

- As with previous low-power DRAM generations, LPDDR4 does not require a delay-locked loop (DLL) or phase-locked loop (PLL)